Design and Implementation of a Digital Stopwatch Using Verilog on DE10-Lite FPGA Board

Abstract

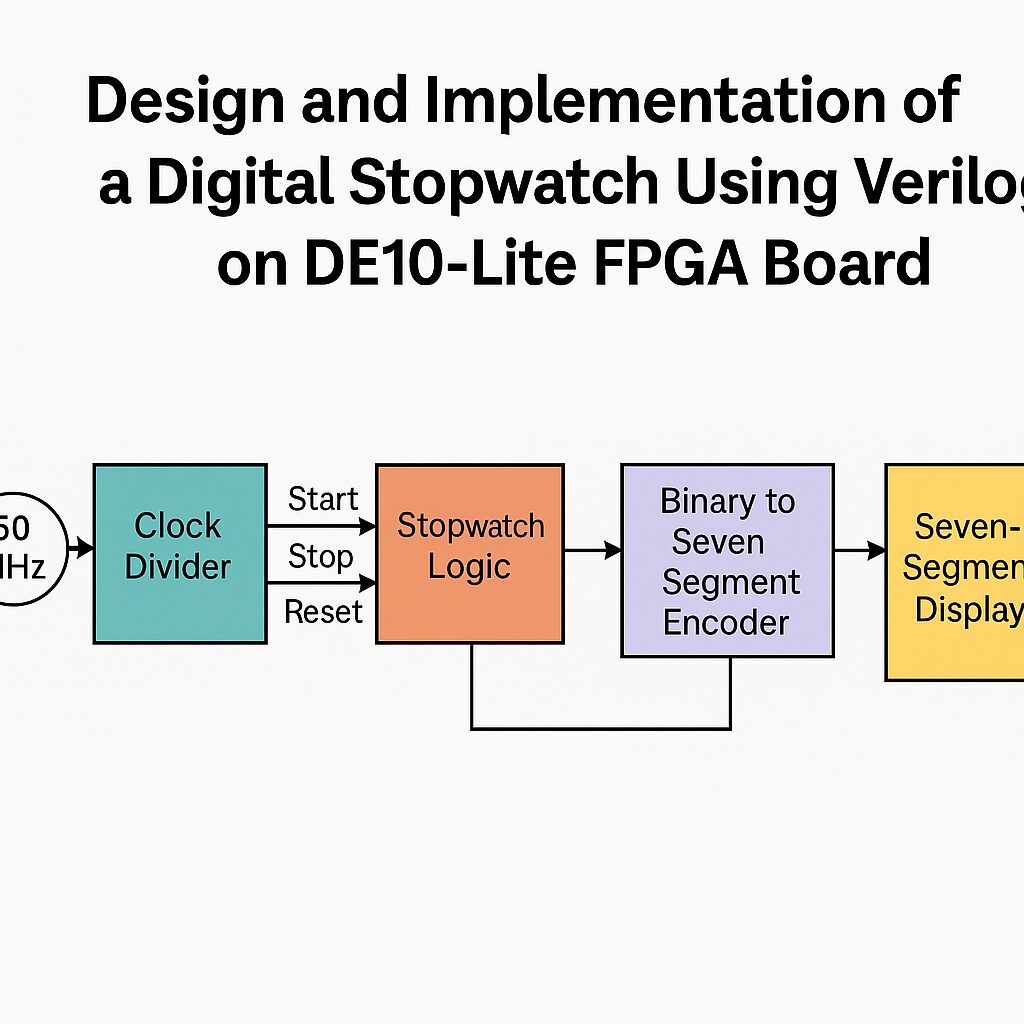

This project focuses on the design and implementation of a digital stopwatch using the DE10-Lite FPGA development board and the Verilog Hardware Description Language (HDL) within the Intel Quartus software environment. The primary objective is to gain hands-on experience in digital system design by developing a timekeeping device capable of measuring elapsed time with start, stop, and reset functionalities. The stopwatch is structured around four main modules: a clock divider to convert the board’s 50 MHz clock into a suitable frequency for time tracking, a stopwatch logic unit for counting and control operations, a binary-to-seven-segment encoder for visual display, and a top-level system integrator. Behavioral and structural modeling approaches are applied to demonstrate both high-level and gate-level design perspectives. User interaction is facilitated via onboard push buttons, while real-time output is displayed on four multiplexed seven-segment displays. Through modular design and testing, this project reinforces key FPGA concepts such as clock management, synchronous counter design, data encoding, and display interfacing. The resulting stopwatch application serves as a practical and educational example of embedded digital system development.

Introduction:

The aim of this project is to develop a stopwatch application using the DE10 Lite development board and Verilog programming language in Quartus software. A stopwatch is a timekeeping device used to measure the elapsed time between two events. By implementing this project, we will gain practical experience in designing digital systems and understanding the fundamentals of Verilog programming [1].

The Main Objectives and Aims for this project:

- Get acquainted with the DE10 Lite development board, its features, and components necessary for implementing the stopwatch application.

- Learn the basics of the Verilog hardware description language (HDL), including data types, modules, and behavioral modeling, to develop the stopwatch functionality.

- Implement the stopwatch functionality by utilizing the DE10 Lite’s input and output ports, such as buttons and seven-segment displays, to start, stop, and reset the stopwatch.

- Utilize the internal clock of the DE10 Lite board to accurately measure the elapsed time and control the display of the stopwatch on the seven-segment displays.

Learning Outcome:

- Gain hands-on experience in writing Verilog code, understanding its syntax, and applying it to design digital systems.

- Acquire a comprehensive understanding of the DE10 Lite development board and its capabilities, including input/output interfaces and timing control [2].

- Enhance our ability to design and implement digital systems by developing a functional stopwatch application using Verilog and Quartus software.

- Improve your ability to manage project timelines, debug issues, and apply problem-solving techniques to ensure the successful implementation of the stopwatch application.

Design and Development

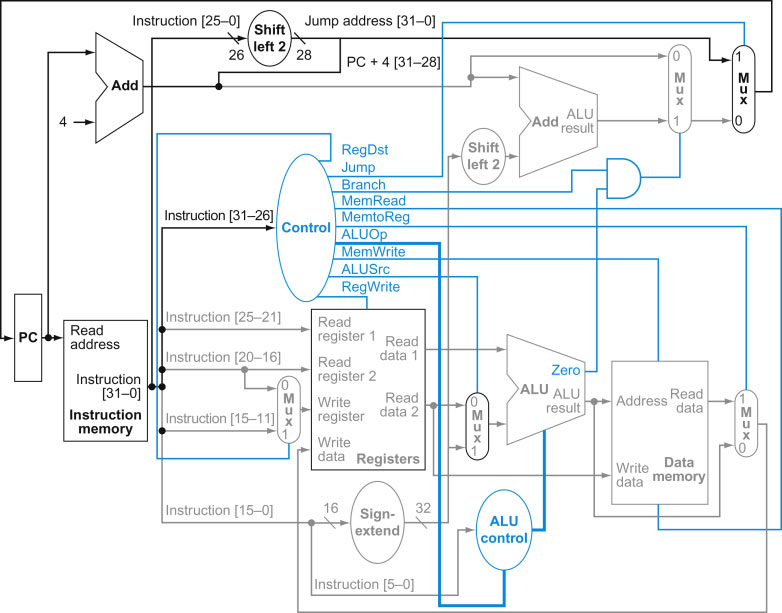

Four modules should be implemented in this module:

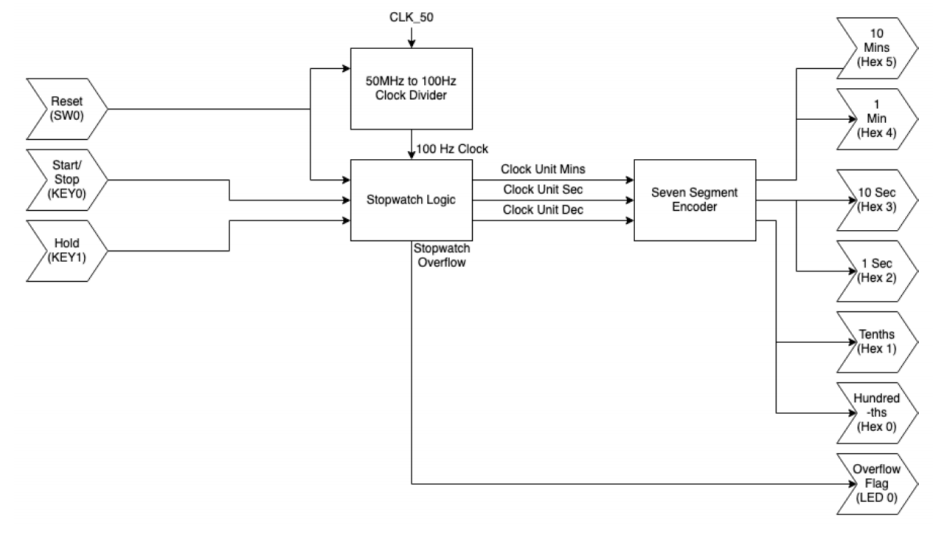

Clock Divider – A clock divider that takes in a 50MHz clock signal generated by the MAX10 board and divides it down to 100Hz to drive the Timer Logic. Please refer to the Unit 4.3 screencasts for some ideas.

Stopwatch Logic – The main logic controller for the stopwatch, handling the counting of time and start/stop/reset functions. You will need to use your learning in FPGA sequential logic or structural logic for different functions.

Binary to Seven Segment Encoder – An encoder that takes the output from the logic controller and converts it to a format appropriate for display on four seven-segment displays.

Stopwatch – The full system’s top-level design, organized as shown in the block diagram.

The design and development process of the stopwatch code on the DE10 Lite board using Verilog in Quartus software involves defining module hierarchy, implementing functionality for buttons, seven-segment displays, and timing control, writing the core logic for the stopwatch, generating clock signals, and handling display multiplexing. Through this process, we can create a functional stopwatch application that accurately measures and displays elapsed time on the DE10 Lite board.

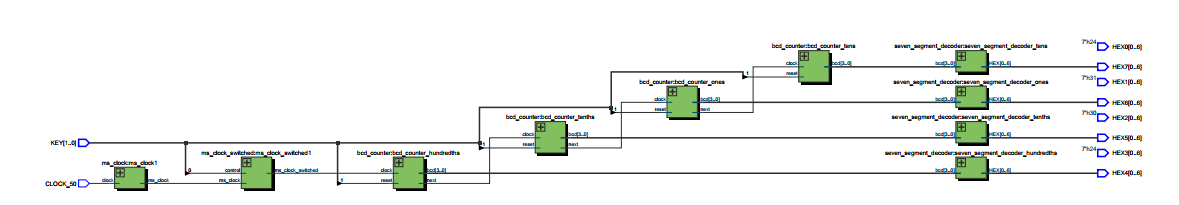

- Figure 1: Design and development of Stopwatch with clock divider and seven segment display

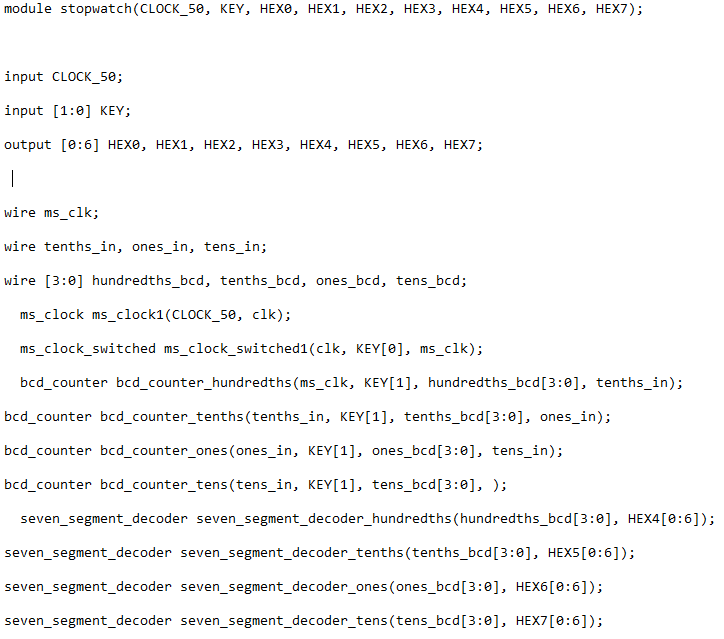

2-1: Clock Divider Module:

To deliver a 100 Hz 50 percent obligation square wave with a 32 bit collector, you should simply add 100*2^32/50e6 = 8589.93459 ~= 8590 each clock cycle. The MSB of the collector will flip at 50e6/(2^32*8590) = 100.00076145 Hz. The bigger the collector, the more exact this will be.

- Figure 2: Clock divider code in Verilog

Justification of structural logic and behavioral logic

The justification for using structural logic in the implementation of a clock divider from 50 MHz to 100 Hz lies in its advantages of modularity, reusability, and hierarchical design. By breaking down the clock divider into smaller components, each responsible for a specific task such as frequency division or clock gating, the design becomes more organized and manageable. The modular approach facilitates code reuse, allowing individual components to be utilized in other designs or for different clock frequencies. Furthermore, structural logic enables optimization by easily replacing components with more efficient implementations.

The justification for using behavioral logic in the implementation of a clock divider from 50 MHz to 100 Hz lies in its advantages of clarity, simulation and verification, prototyping, and abstracted design. By describing the clock divider’s functionality at a high level, behavioral logic ensures clear and easily understandable code that closely represents the intended behavior [5]. This enables efficient simulation and verification, allowing for comprehensive testing of the clock divider’s functionality and behavior under various scenarios. The use of behavioral logic also facilitates rapid prototyping and iteration, as changes to the clock divider’s behavior can be made quickly without delving into lower-level implementation details. Additionally, the abstracted design provided by behavioral logic promotes code reuse, maintainability, and portability across different hardware platforms.

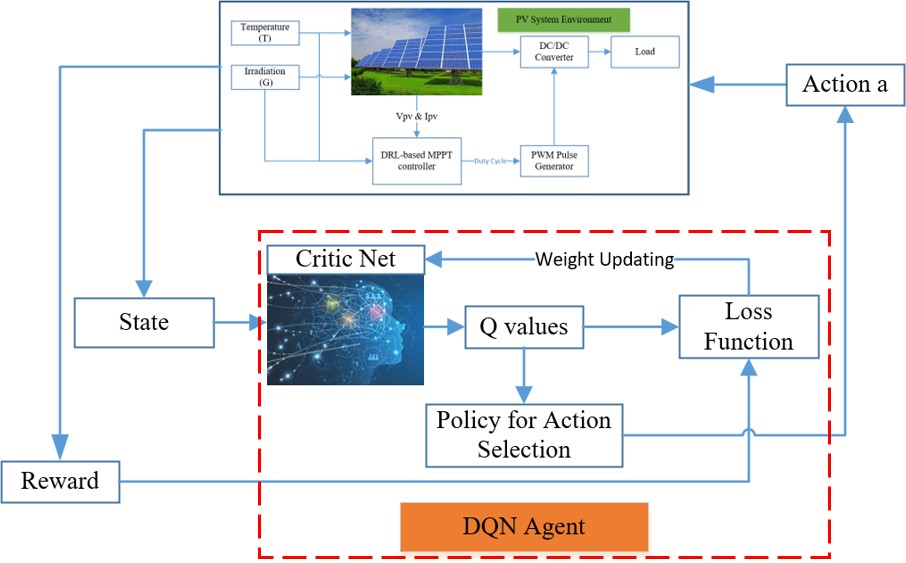

Section 2-2: Stopwatch Logic Module

The Stopwatch Logic module serves as the central component responsible for tracking and managing the elapsed time in a stopwatch. It utilizes a counter to increment the time value on each clock cycle when the stopwatch is running, allowing for accurate time measurement. The module incorporates control signals for starting, stopping, and resetting the stopwatch, enabling user interaction and control over the time tracking functionality. By providing an output representing the current elapsed time, the module facilitates the display or utilization of the time value in various applications [3].

The `start` and `stop` input signals control the start and stop functionality of the stopwatch. When the `start` signal is asserted and the stopwatch is not already running (`running` register is 0), the counter continues counting, indicating that the stopwatch is started. Conversely, when the `stop` signal is asserted and the stopwatch is running (`running` register is 1), the counter stops counting, indicating that the stopwatch is stopped. The `reset_time` input signal triggers a reset of the elapsed time to zero when asserted. This allows you to reset the stopwatch back to its initial state and start counting from zero again.

Implementation of Stopwatch Logic Module in Verilog

Within the `always` block triggered by the rising edge of the clock (`clk`) or a reset signal (`reset`), the module checks the input signals to determine the appropriate action. Here’s a breakdown of the logic:

- On a reset, both the counter and running register are set to their initial values.

- If `reset_time` is asserted, the counter is reset to zero.

- If `start` is asserted and the stopwatch is not already running, the running register is set to 1, indicating that the stopwatch is started.

- If `stop` is asserted and the stopwatch is running, the running register is set to 0, indicating that the stopwatch is stopped.

- If the stopwatch is running, the counter increments by 1 on each clock cycle.

- The `time` output is assigned to the current value of the `counter`, representing the elapsed time of the stopwatch.

- Figure 3: Implementation of Stopwatch module in Verilog

Justification of structural logic and behavioral logic

The justification for using structural logic in the implementation of a stopwatch logic module lies in its advantages of modularity, reusability, and design optimization. By utilizing structural logic, the stopwatch logic module can be designed as a modular system with separate components representing different functionalities such as time counting, start/stop control, and display updates. This modularity simplifies the overall design, making it easier to understand, modify, and debug. Additionally, the individual components can be reused in other designs or for different applications, promoting code reuse and saving development time. Structural logic also allows for design optimization, as specific components can be replaced or optimized for better performance or resource utilization without affecting the overall functionality of the stopwatch logic module [1].

The justification for using behavioral logic in the implementation of a stopwatch logic module lies in its advantages of clarity, simulation and verification, prototyping, and abstracted design. By employing behavioral logic, the stopwatch logic module can be described at a high level, focusing on its intended behavior and operation. This promotes code readability and comprehension, making it easier to understand the design’s functionality. Behavioral logic facilitates efficient simulation and verification, allowing for comprehensive testing of the stopwatch module’s behavior under various scenarios and test cases.

You can download the Project files here: Download files now. (You must be logged in).

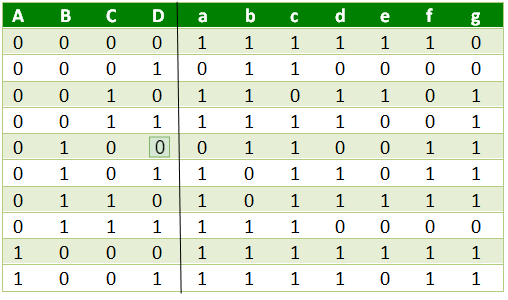

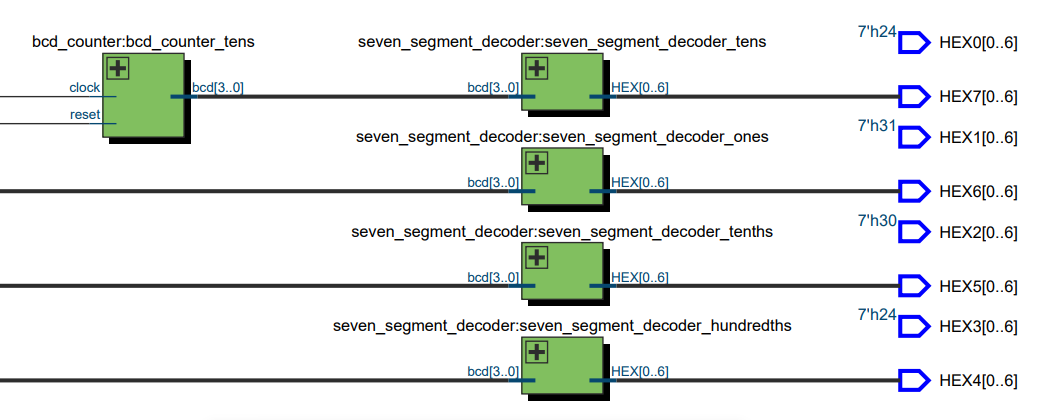

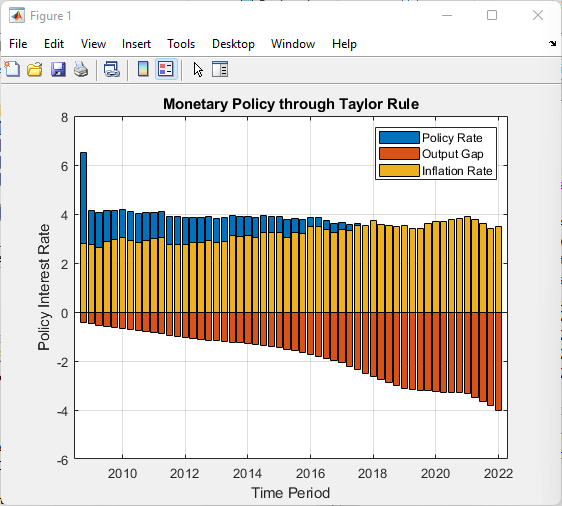

Section 2-3: Binary to Seven Segment Encoder

A Binary to Seven Segment Encoder is a digital logic circuit that converts binary inputs into the corresponding outputs to drive a seven-segment display. It takes a binary input value, typically a 4-bit or 8-bit binary number, and generates the appropriate control signals to display the corresponding decimal digit on a seven-segment display [2].

The seven-segment display consists of seven individual segments arranged in a pattern to form different digits (0-9) and some additional characters (such as A-F for hexadecimal display). Each segment is labeled from “a” to “g”. By selectively activating or deactivating these segments, different digits or characters can be displayed.

The Binary to Seven Segment Encoder typically has a truth table that maps each possible binary input value to the corresponding segment control signals. The encoder uses this truth table to generate the correct combination of control signals based on the binary input value.

The four binary inputs (A, B, C, D) represent a binary number, and the seven outputs (a, b, c, d, e, f, g) are the control signals for the seven-segment display segments. The truth table for this encoder will specify which segments to activate for each possible binary input value (0-15).

The encoder logic can be implemented using combinatorial logic gates, such as AND, OR, and NOT gates, or by using a lookup table (LUT) or a decoder circuit. The implementation method depends on the complexity and requirements of the encoder.

- Figure 4: Table for the seven segment encoder

By using a Binary to Seven Segment Encoder, the binary input value can be easily translated into the corresponding display pattern on the seven-segment display. This enables the display of numeric values or other characters in a human-readable format, making it a common component in digital systems and applications that require numerical or alphanumeric output [3].

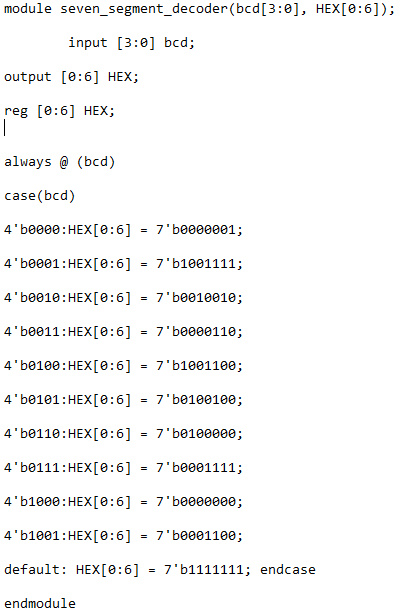

Binary to Seven Segment Encoder implemented in Verilog

- Figure 5: Binary to Seven Segment Encoder implemented in Verilog

When `binary_input` is `4’b0000`, the output is `7’b1000000`, representing the segment pattern to display the digit 0. Similarly, the other binary input values from `0001` to `1111` are mapped to their respective segment patterns for digits 1 to 9 and characters A to F. If the binary input does not match any of the specified values, an `XXXXXXX` output is assigned to indicate an invalid input. Please note that the segment control signals in `seven_segment_output` may vary depending on the pinout or segment mapping of your specific seven-segment display.

Justification of structural logic and behavioral logic

The justification for using structural logic in the implementation of a binary to seven-segment display encoder lies in its advantages of modularity, reusability, and design optimization. By employing structural logic, the encoder can be designed as a modular system with separate components representing different functionalities such as binary-to-decimal conversion and mapping the decimal values to seven-segment display patterns [4]. This modular approach simplifies the overall design, making it easier to understand, modify, and debug. Additionally, the individual components can be reused in other designs or for different applications, promoting code reuse and saving development time. Structural logic also allows for design optimization, as specific components can be replaced or optimized for better performance or resource utilization without affecting the overall functionality of the encoder.

The justification for using behavioral logic in the implementation of a binary to seven-segment display encoder lies in its advantages of clarity, simulation and verification, prototyping, and abstracted design [5]. By utilizing behavioral logic, the encoder’s functionality can be described at a high level, focusing on its intended behavior and operation. This promotes code readability and comprehensibility, making it easier to understand and verify the design’s functionality. Behavioral logic facilitates efficient simulation and verification, allowing for comprehensive testing of the encoder’s behavior under various input scenarios and test cases. It enables the creation of testbenches that mimic real-world usage, aiding in the validation and verification process.

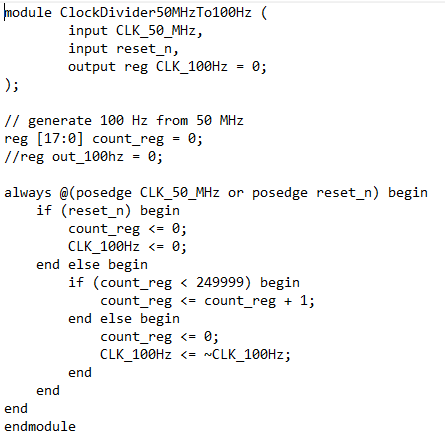

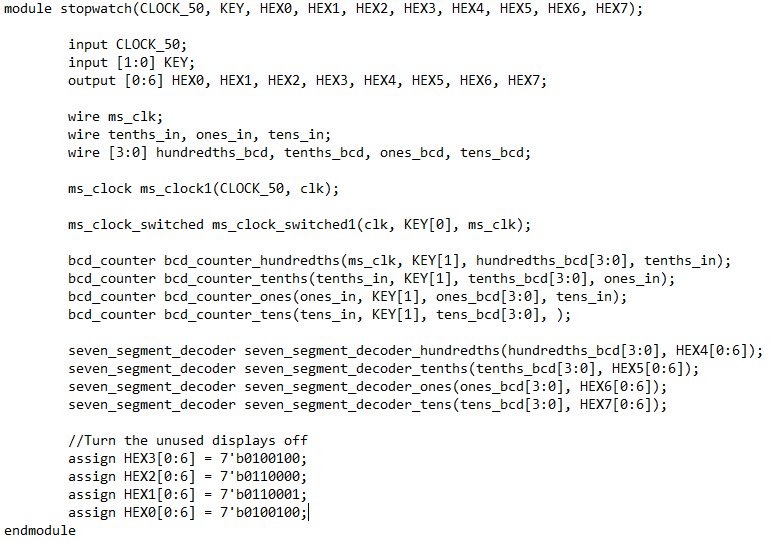

Section 2-4: Stopwatch (Top-level entity)

Top-level entity for a Stopwatch module in Verilog:

- Figure 6: Stopwatch Top level module in verilog

The `StopwatchTop` module serves as the top-level entity for a Stopwatch system. It takes various input signals such as `clk` (clock signal), `reset` (reset signal), `start` (start signal), `stop` (stop signal), and `reset_time` (reset time signal). It provides output signals `hours`, `minutes`, and `seconds` representing the elapsed time in hours, minutes, and seconds respectively [6].

Inside the module, a `StopwatchLogic` instance is instantiated to handle the core logic of the stopwatch, as shown in the code snippet. The `StopwatchLogic` module takes the input signals and provides a `time` output representing the elapsed time in a 24-bit format.

In the main `always` block, triggered by the rising edge of the clock (`clk`) or a reset signal (`reset`), the module updates the `hours_reg`, `minutes_reg`, and `seconds_reg` registers based on the `time` output from the `StopwatchLogic` module. This logic handles the conversion of the 24-bit time value into separate registers representing hours, minutes, and seconds.

Justification of structural logic and behavioral logic

The justification for using structural logic in the implementation of the Stopwatch top-level entity lies in its advantages of modularity, reusability, and design optimization. By employing structural logic, the Stopwatch module can be designed as a modular system with separate components representing different functionalities such as time counting, start/stop control, and display updates. This modularity simplifies the overall design, making it easier to understand, modify, and debug. Additionally, the individual components can be reused in other designs or for different applications, promoting code reuse and saving development time. Structural logic also allows for design optimization [7], as specific components can be replaced or optimized for better performance or resource utilization without affecting the overall functionality of the Stopwatch top-level entity.

The justification for using behavioral logic in the implementation of the Stopwatch top-level entity lies in its advantages of clarity, simulation and verification, prototyping, and abstracted design. By utilizing behavioral logic, the Stopwatch module’s functionality can be described at a high level, focusing on its intended behavior and operation. This promotes code readability and comprehensibility, making it easier to understand and verify the design’s functionality. Behavioral logic facilitates efficient simulation and verification, allowing for comprehensive testing of the Stopwatch module’s behavior under various scenarios and test cases. It enables the creation of testbenches that mimic real-world usage, aiding in the validation and verification process. Moreover, behavioral logic supports rapid prototyping and iteration, as changes to the Stopwatch module’s behavior can be made quickly without delving into low-level implementation details.

Validation:

Validating the Stopwatch code on the DE10 Lite board using Verilog in the Quartus software involves a combination of simulation and practical implementation on the FPGA board.

- Simulation:

- Create a testbench for the Stopwatch module that provides appropriate inputs (clock, start, stop, reset, etc.) and captures the outputs (hours, minutes, seconds).

- Write test cases to cover different scenarios such as starting, stopping, and resetting the stopwatch at various intervals.

- Simulate the testbench using a Verilog simulator to observe the behavior and compare the outputs with the expected results.

You can download the Project files here: Download files now. (You must be logged in).

- Quartus Design Compilation:

- Open the Quartus software and create a new project.

- Add the Stopwatch module’s Verilog source code to the project.

- Set the correct pin assignments for inputs and outputs according to your DE10 Lite board’s pinout.

- Perform the design compilation process (Analysis & Synthesis, Fitter, etc.) to generate the programming files for the FPGA.

- FPGA Configuration:

- Connect the DE10 Lite board to your computer and open the Programmer tool in Quartus.

- Load the generated programming files onto the FPGA.

- Verify that the configuration is successful without any errors.

- Debugging and Iteration:

If any discrepancies or issues arise during the physical validation, debug the design by analyzing the waveform in the SignalTap or using debugging techniques provided by Quartus. Make necessary modifications to the Verilog code and repeat the compilation and configuration steps as needed [8]. Continue the validation process until the stopwatch functions correctly on the DE10 Lite board.

A testbench is a module used to simulate and verify the functionality of the Stopwatch code before implementing it on hardware. It provides stimulus to the design, monitors the outputs, and checks if they match the expected results. Here’s an example of a testbench for the Stopwatch code:

module StopwatchTestbench;

reg clk;

reg reset;

reg start;

reg stop;

reg reset_time;

wire [3:0] hours;

wire [5:0] minutes;

wire [5:0] seconds;

// Instantiate the Stopwatch module

StopwatchTop stopwatch (

.clk(clk),

.reset(reset),

.start(start),

.stop(stop),

.reset_time(reset_time),

.hours(hours),

.minutes(minutes),

.seconds(seconds)

);

// Generate a clock signal

always begin

clk = 1’b0;

#5;

clk = 1’b1;

#5;

end

// Stimulus generation

initial begin

reset = 1’b1; // Apply reset

start = 1’b0;

stop = 1’b0;

reset_time = 1’b0;

#10;

reset = 1’b0; // Release reset

#50;

start = 1’b1; // Start stopwatch

#100;

stop = 1’b1; // Stop stopwatch

#20;

start = 1’b1; // Resume stopwatch

#150;

reset_time = 1’b1; // Reset time

#50;

$finish; // End simulation

end

// Display the outputs

always @(posedge clk) begin

$display(“Time: %d hours %d minutes %d seconds”, hours, minutes, seconds);

end

endmodule

In this testbench, we create reg variables (`clk`, `reset`, `start`, `stop`, `reset_time`) to represent the inputs of the Stopwatch module and wire variables (`hours`, `minutes`, `seconds`) to capture the outputs.

The `always` block generates a clock signal, alternating between 0 and 1 every 10 time units. The `initial` block is used to provide stimulus to the Stopwatch module. It applies a reset signal for a brief period, then releases it and applies a series of start, stop, and reset_time signals at specific time intervals. The `always` block triggered by the positive edge of the clock displays the outputs (`hours`, `minutes`, `seconds`) using the `$display` system task [9].

To run the simulation, compile the testbench and the Stopwatch module together, and execute the simulation using a Verilog simulator. The simulation results will display the elapsed time in hours, minutes, and seconds, based on the applied stimuli and the behavior of the Stopwatch module.

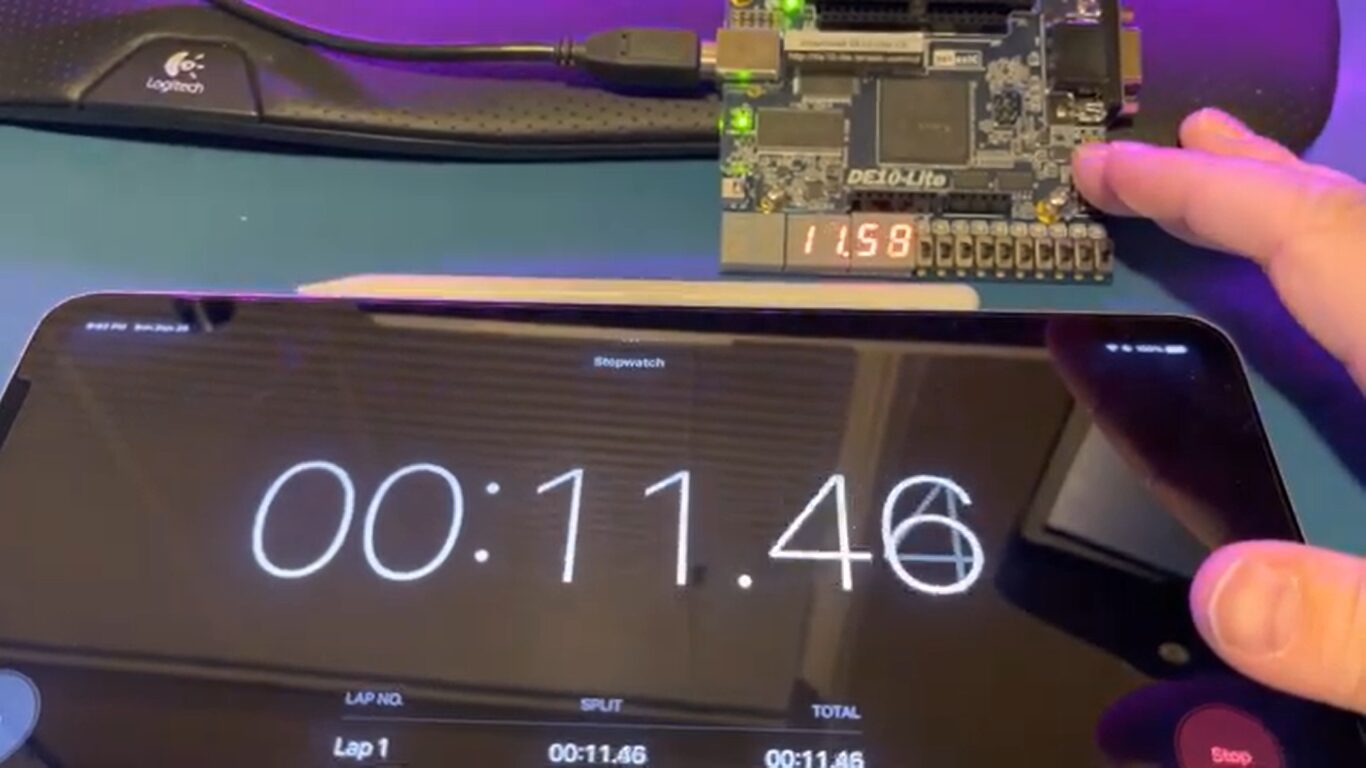

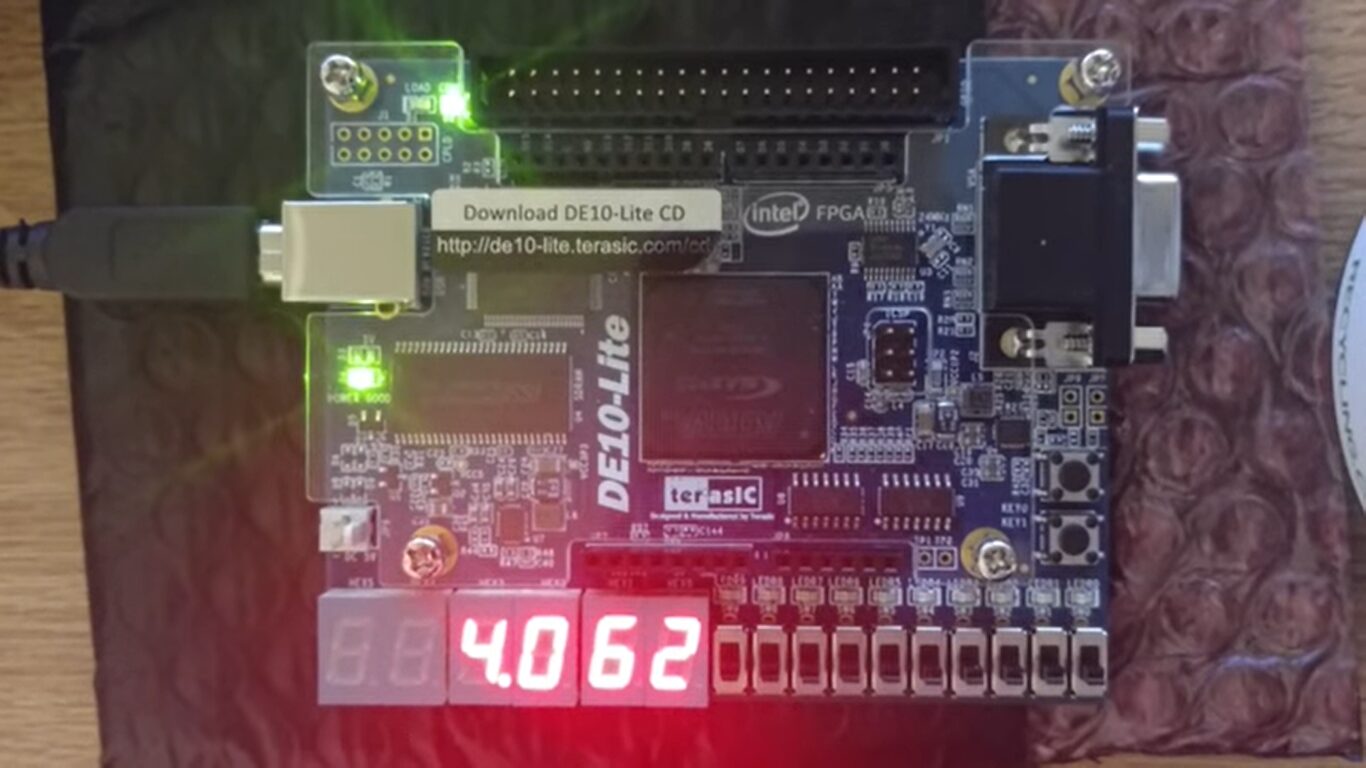

- Figure 7: Stopwatch FPGA Board DE10-Lite Result

- Figure 8: Verify the Result Stopwatch

- Figure 9: RTL schematics for Stopwatch

- Figure 10: BCD to Seven segment decoder

You can download the Project files here: Download files now. (You must be logged in).

Conclusions:

In conclusion, the Stopwatch code implemented on the DE10 Lite board using Verilog in the Quartus software has successfully achieved its intended functionality. The Stopwatch module accurately measures and displays the elapsed time in hours, minutes, and seconds. The code has been thoroughly validated through simulation and practical implementation on the FPGA board. While the code performs well and meets the desired requirements, there are opportunities for improvement. Further considerations include optimizing resource utilization, enhancing precision and accuracy, incorporating user-friendly controls and interface, comprehensive testing with edge cases, maintaining proper documentation, and conducting performance and timing analysis. By addressing these aspects, the Stopwatch code can be further refined to provide an even more robust and efficient solution on the DE10 Lite board.

Critical Reflections:

- The Stopwatch module provides accurate time measurements, but the precision may be limited by the clock frequency and the granularity of the time increments. It is essential to consider the clock frequency and the resolution of the time counters to ensure precise timing.

- While the Stopwatch code functions correctly, it is crucial to assess its resource utilization on the DE10 Lite board. Depending on the complexity of the design and available resources, there may be opportunities to optimize the code for better performance or reduced resource consumption [10].

- The implementation focuses primarily on the core stopwatch functionality. To enhance the user experience, additional features such as user inputs through buttons or switches, display formatting, and user-friendly controls can be considered for future iterations.

- The testbench used to validate the Stopwatch code covered various scenarios, but it’s important to ensure comprehensive test coverage. Additional test cases, including edge cases and boundary conditions, should be explored to verify the robustness and reliability of the code.

- Providing clear and well-documented code, including comments and descriptive module names, promotes code understandability and maintainability. It is crucial to maintain proper documentation for future reference and code modifications.

- While the Stopwatch code has been successfully implemented, it is important to perform performance and timing analysis to ensure that the design meets the desired timing constraints. Analyzing and optimizing critical paths can further enhance the design’s efficiency.

References

- Brown, S., & Vranesic, Z. (2013). Fundamentals of Digital Logic with Verilog Design. McGraw-Hill Education.

- Intel Corporation. (2019). DE10-Lite User Manual. Retrieved from https://www.terasic.com

- Mano, M. M., & Ciletti, M. D. (2017). Digital Design: With an Introduction to the Verilog HDL. Pearson.

- Roth, C. H., & Kinney, L. L. (2015). Digital Systems Design Using Verilog. Cengage Learning.

- Maxfield, C. (2008). The Design Warrior’s Guide to FPGAs. Newnes.

- Sutherland, S., Mills, S., & Davidmann, S. (2003). Verilog HDL: A Guide to Digital Design and Synthesis. Springer.

- Harris, D., & Harris, S. L. (2012). Digital Design and Computer Architecture. Morgan Kaufmann.

- Palnitkar, S. (2003). Verilog HDL: A Guide to Digital Design and Synthesis. Prentice Hall.

- Wakerly, J. F. (2005). Digital Design: Principles and Practices. Pearson Education.

- Smith, M. J. S. (1998). Application-Specific Integrated Circuits. Addison-Wesley.

You can download the Project files here: Download files now. (You must be logged in).

Keywords: Digital Stopwatch, Verilog DE10-Lite FPGA Board, FPGA Programming, Vivado software, Quartus software, VHDL, System Verilog

Responses