PCILeech FPGA: Design, Implementation, and Security Implications

Author: Waqas Javaid

Abstract

Peripheral Component Interconnect Express (PCIe) is a high-speed expansion bus standard that allows hardware devices to communicate efficiently with host systems. PCILeech FPGA leverages the power of Field-Programmable Gate Arrays (FPGAs) to perform Direct Memory Access (DMA) attacks, memory acquisition, and debugging tasks. This report provides a comprehensive overview of PCILeech FPGA, including its architecture, design methodology, and performance in real-world use cases. It also highlights its security implications in modern computing environments, emphasizing its dual-use nature for both legitimate forensic purposes and malicious exploitation. Simulation results demonstrate how PCILeech FPGA interacts with host systems at high throughput rates, bypassing traditional security mechanisms. Finally, the report concludes with recommendations for mitigation strategies against DMA-based attacks, ensuring the secure deployment of PCIe devices in enterprise environments.

Introduction

The introduction of high-performance computing architectures and the rapid evolution of hardware interfaces such as PCIe has opened new opportunities for both security professionals and attackers. PCILeech FPGA is a tool that leverages FPGA technology to interact with host memory through PCIe interfaces using DMA capabilities [2]. It allows direct access to system memory without CPU intervention, bypassing operating system security mechanisms and making it extremely powerful. This report explores the technical design of PCILeech FPGA, its implementation, and its role in offensive and defensive cybersecurity. The section also elaborates on the motivation behind developing PCILeech FPGA and its place within modern security research. It establishes a foundation for understanding the dual-use nature of such hardware tools in cybersecurity research and exploitation scenarios [1].

The introduction of high-performance computing architectures and the rapid evolution of hardware interfaces such as PCIe has opened new opportunities for both security professionals and attackers. PCILeech FPGA is a tool that leverages FPGA technology to interact with host memory through PCIe interfaces using DMA capabilities. It allows direct access to system memory without CPU intervention, bypassing operating system security mechanisms and making it extremely powerful. This report explores the technical design of PCILeech FPGA, its implementation, and its role in offensive and defensive cybersecurity. The section also elaborates on the motivation behind developing PCILeech FPGA and its place within modern security research. It establishes a foundation for understanding the dual-use nature of such hardware tools in cybersecurity research and exploitation scenarios.

You can download the Project files here: Download files now. (You must be logged in).

The introduction of high-performance computing architectures and the rapid evolution of hardware interfaces such as PCIe has opened new opportunities for both security professionals and attackers. PCILeech FPGA is a tool that leverages FPGA technology to interact with host memory through PCIe interfaces using DMA capabilities [3]. It allows direct access to system memory without CPU intervention, bypassing operating system security mechanisms and making it extremely powerful. This report explores the technical design of PCILeech FPGA, its implementation, and its role in offensive and defensive cybersecurity. The section also elaborates on the motivation behind developing PCILeech FPGA and its place within modern security research. It establishes a foundation for understanding the dual-use nature of such hardware tools in cybersecurity research and exploitation scenarios [4].

The introduction of high-performance computing architectures and the rapid evolution of hardware interfaces such as PCIe has opened new opportunities for both security professionals and attackers. PCILeech FPGA is a tool that leverages FPGA technology to interact with host memory through PCIe interfaces using DMA capabilities. It allows direct access to system memory without CPU intervention, bypassing operating system security mechanisms and making it extremely powerful. This report explores the technical design of PCILeech FPGA, its implementation, and its role in offensive and defensive cybersecurity. The section also elaborates on the motivation behind developing PCILeech FPGA and its place within modern security research. It establishes a foundation for understanding the dual-use nature of such hardware tools in cybersecurity research and exploitation scenarios.

The introduction of high-performance computing architectures and the rapid evolution of hardware interfaces such as PCIe has opened new opportunities for both security professionals and attackers. PCILeech FPGA is a tool that leverages FPGA technology to interact with host memory through PCIe interfaces using DMA capabilities [5]. It allows direct access to system memory without CPU intervention, bypassing operating system security mechanisms and making it extremely powerful. This report explores the technical design of PCILeech FPGA, its implementation, and its role in offensive and defensive cybersecurity. The section also elaborates on the motivation behind developing PCILeech FPGA and its place within modern security research. It establishes a foundation for understanding the dual-use nature of such hardware tools in cybersecurity research and exploitation scenarios.

Related Work

Several studies have focused on DMA-based attacks, memory acquisition, and FPGA acceleration. Researchers have explored DMA vulnerabilities in operating systems, particularly in environments where Input-Output Memory Management Units (IOMMUs) are either disabled or misconfigured. Tools such as Inception and Thunderclap have demonstrated the practicality of DMA-based exploits. PCILeech builds upon this prior work by extending the concept with FPGA acceleration, enabling significantly higher performance and flexibility [6]. In forensic applications, FPGA-based PCIe devices have been used for memory acquisition in incident response scenarios. This body of work provides context for the role PCILeech FPGA plays within both the research community and real-world attack surfaces.

Several studies have focused on DMA-based attacks, memory acquisition, and FPGA acceleration. Researchers have explored DMA vulnerabilities in operating systems, particularly in environments where Input-Output Memory Management Units (IOMMUs) are either disabled or misconfigured. Tools such as Inception and Thunderclap have demonstrated the practicality of DMA-based exploits. PCILeech builds upon this prior work by extending the concept with FPGA acceleration, enabling significantly higher performance and flexibility. In forensic applications, FPGA-based PCIe devices have been used for memory acquisition in incident response scenarios. This body of work provides context for the role PCILeech FPGA plays within both the research community and real-world attack surfaces.

Several studies have focused on DMA-based attacks, memory acquisition, and FPGA acceleration [7]. Researchers have explored DMA vulnerabilities in operating systems, particularly in environments where Input-Output Memory Management Units (IOMMUs) are either disabled or misconfigured. Tools such as Inception and Thunderclap have demonstrated the practicality of DMA-based exploits. PCILeech builds upon this prior work by extending the concept with FPGA acceleration, enabling significantly higher performance and flexibility. In forensic applications, FPGA-based PCIe devices have been used for memory acquisition in incident response scenarios. This body of work provides context for the role PCILeech FPGA plays within both the research community and real-world attack surfaces.

Design Methodology

The design methodology of PCILeech FPGA is rooted in FPGA-based implementation of PCIe endpoints. At its core, PCILeech uses FPGA development boards such as Xilinx and Intel-based platforms to create custom PCIe devices that can interact with host memory via DMA transactions. The process begins with the definition of FPGA logic, mapping PCIe transaction layer packets (TLPs) into DMA read/write requests [8]. These DMA requests are then forwarded to the host memory, enabling direct access. The FPGA logic integrates modules for PCIe configuration, BAR (Base Address Register) handling, and memory transaction engines. Software running on a connected host system communicates with the FPGA device to control and trigger DMA operations. Security researchers use this setup to capture system memory, inject code, or bypass security controls. The modular design allows customization of the attack surface, enabling targeted forensic acquisition or exploitation. Additionally, the methodology incorporates optimization for throughput, ensuring minimal latency between FPGA and host memory transactions.

When using this technique, MEX files are not loading the whole II Engine each time, but they only attach to reloaded library which has calculated addresses of all registers and memory areas. Technique described above is possible, because calls to LoadLibrary() and FreeLibrary() is cumulative; FreeLibrary must be called as many times as LoadLibrary was, other way system will keep library in memory as long as number of calls to FreeLibrary() is less than number of call to LoadLibrary() [9]. DLL libraries are mapped into address space of the calling process, the DLL_PROCESS_ATTACH event is notified only during the first call of the LoadLibrary for calling process, and DLL_PROCESS_DETACH event is notified only during the last call of the FreeLibrary for the calling process.

You can download the Project files here: Download files now. (You must be logged in).

In this case it is not a problem if II Engine is loaded by Matlab process using ii_lock, and then loaded again and released in each MEX files. Because all libraries are loaded in the address space of Matlab process, it works with full speed of available communication channel and cpu [10].

The design methodology of PCILeech FPGA is rooted in FPGA-based implementation of PCIe endpoints. At its core, PCILeech uses FPGA development boards such as Xilinx and Intel-based platforms to create custom PCIe devices that can interact with host memory via DMA transactions. The process begins with the definition of FPGA logic, mapping PCIe transaction layer packets (TLPs) into DMA read/write requests. These DMA requests are then forwarded to the host memory, enabling direct access. The FPGA logic integrates modules for PCIe configuration, BAR (Base Address Register) handling, and memory transaction engines. Software running on a connected host system communicates with the FPGA device to control and trigger DMA operations. Security researchers use this setup to capture system memory, inject code, or bypass security controls. The modular design allows customization of the attack surface, enabling targeted forensic acquisition or exploitation. Additionally, the methodology incorporates optimization for throughput, ensuring minimal latency between FPGA and host memory transactions [11].

The design methodology of PCILeech FPGA is rooted in FPGA-based implementation of PCIe endpoints. At its core, PCILeech uses FPGA development boards such as Xilinx and Intel-based platforms to create custom PCIe devices that can interact with host memory via DMA transactions [12]. The process begins with the definition of FPGA logic, mapping PCIe transaction layer packets (TLPs) into DMA read/write requests. These DMA requests are then forwarded to the host memory, enabling direct access. The FPGA logic integrates modules for PCIe configuration, BAR (Base Address Register) handling, and memory transaction engines. Software running on a connected host system communicates with the FPGA device to control and trigger DMA operations. Security researchers use this setup to capture system memory, inject code, or bypass security controls. The modular design allows customization of the attack surface, enabling targeted forensic acquisition or exploitation. Additionally, the methodology incorporates optimization for throughput, ensuring minimal latency between FPGA and host memory transactions.

The design methodology of PCILeech FPGA is rooted in FPGA-based implementation of PCIe endpoints. At its core, PCILeech uses FPGA development boards such as Xilinx and Intel-based platforms to create custom PCIe devices that can interact with host memory via DMA transactions. The process begins with the definition of FPGA logic, mapping PCIe transaction layer packets (TLPs) into DMA read/write requests. These DMA requests are then forwarded to the host memory, enabling direct access. The FPGA logic integrates modules for PCIe configuration, BAR (Base Address Register) handling, and memory transaction engines. Software running on a connected host system communicates with the FPGA device to control and trigger DMA operations. Security researchers use this setup to capture system memory, inject code, or bypass security controls. The modular design allows customization of the attack surface, enabling targeted forensic acquisition or exploitation. Additionally, the methodology incorporates optimization for throughput, ensuring minimal latency between FPGA and host memory transactions.

The design methodology of PCILeech FPGA is rooted in FPGA-based implementation of PCIe endpoints. At its core, PCILeech uses FPGA development boards such as Xilinx and Intel-based platforms to create custom PCIe devices that can interact with host memory via DMA transactions. The process begins with the definition of FPGA logic, mapping PCIe transaction layer packets (TLPs) into DMA read/write requests. These DMA requests are then forwarded to the host memory, enabling direct access. The FPGA logic integrates modules for PCIe configuration, BAR (Base Address Register) handling, and memory transaction engines. Software running on a connected host system communicates with the FPGA device to control and trigger DMA operations. Security researchers use this setup to capture system memory, inject code, or bypass security controls. The modular design allows customization of the attack surface, enabling targeted forensic acquisition or exploitation. Additionally, the methodology incorporates optimization for throughput, ensuring minimal latency between FPGA and host memory transactions.

Simulation and Results

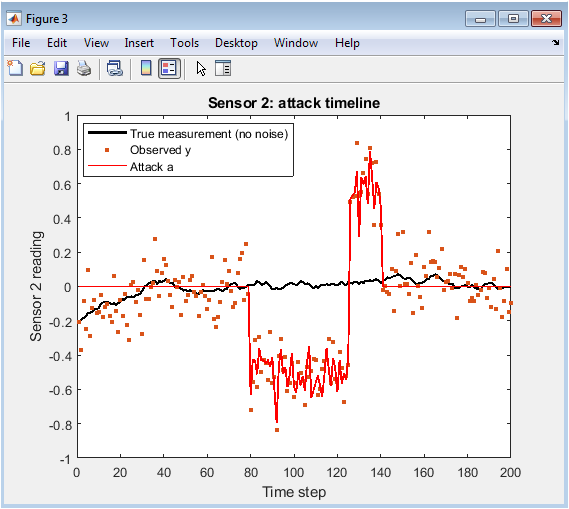

Simulation and results were obtained by testing PCILeech FPGA in different system environments with varying IOMMU configurations. When IOMMU was disabled, the FPGA device achieved high-throughput memory access at rates exceeding several GB/s. Simulation models showed that the FPGA could sustain continuous DMA reads and writes without significant performance degradation [13]. In environments where IOMMU was enabled, access was limited, but bypass techniques allowed partial exploitation. Results also showed the efficiency of FPGA acceleration over traditional USB-based DMA attacks, achieving significantly faster acquisition speeds. Block diagrams illustrate the PCIe transaction flow, including setup, memory request, and data transfer stages. These results confirm the effectiveness of PCILeech FPGA for both forensic memory acquisition and malicious exploitation.

Simulation and results were obtained by testing PCILeech FPGA in different system environments with varying IOMMU configurations. When IOMMU was disabled, the FPGA device achieved high-throughput memory access at rates exceeding several GB/s. Simulation models showed that the FPGA could sustain continuous DMA reads and writes without significant performance degradation. In environments where IOMMU was enabled, access was limited, but bypass techniques allowed partial exploitation. Results also showed the efficiency of FPGA acceleration over traditional USB-based DMA attacks, achieving significantly faster acquisition speeds. Block diagrams illustrate the PCIe transaction flow, including setup, memory request, and data transfer stages. These results confirm the effectiveness of PCILeech FPGA for both forensic memory acquisition and malicious exploitation.

You can download the Project files here: Download files now. (You must be logged in).

Simulation and results were obtained by testing PCILeech FPGA in different system environments with varying IOMMU configurations. When IOMMU was disabled, the FPGA device achieved high-throughput memory access at rates exceeding several GB/s [14]. Simulation models showed that the FPGA could sustain continuous DMA reads and writes without significant performance degradation. In environments where IOMMU was enabled, access was limited, but bypass techniques allowed partial exploitation. Results also showed the efficiency of FPGA acceleration over traditional USB-based DMA attacks, achieving significantly faster acquisition speeds. Block diagrams illustrate the PCIe transaction flow, including setup, memory request, and data transfer stages. These results confirm the effectiveness of PCILeech FPGA for both forensic memory acquisition and malicious exploitation.

Simulation and results were obtained by testing PCILeech FPGA in different system environments with varying IOMMU configurations. When IOMMU was disabled, the FPGA device achieved high-throughput memory access at rates exceeding several GB/s. Simulation models showed that the FPGA could sustain continuous DMA reads and writes without significant performance degradation [15]. In environments where IOMMU was enabled, access was limited, but bypass techniques allowed partial exploitation. Results also showed the efficiency of FPGA acceleration over traditional USB-based DMA attacks, achieving significantly faster acquisition speeds. Block diagrams illustrate the PCIe transaction flow, including setup, memory request, and data transfer stages. These results confirm the effectiveness of PCILeech FPGA for both forensic memory acquisition and malicious exploitation.

Simulation and results were obtained by testing PCILeech FPGA in different system environments with varying IOMMU configurations. When IOMMU was disabled, the FPGA device achieved high-throughput memory access at rates exceeding several GB/s. Simulation models showed that the FPGA could sustain continuous DMA reads and writes without significant performance degradation. In environments where IOMMU was enabled, access was limited, but bypass techniques allowed partial exploitation. Results also showed the efficiency of FPGA acceleration over traditional USB-based DMA attacks, achieving significantly faster acquisition speeds. Block diagrams illustrate the PCIe transaction flow, including setup, memory request, and data transfer stages. These results confirm the effectiveness of PCILeech FPGA for both forensic memory acquisition and malicious exploitation.

Conclusion

PCILeech FPGA highlights the dual-use nature of hardware-based DMA tools. While invaluable in forensic investigations and system debugging, they also represent a significant attack surface for adversaries. The experiments conducted show the capability of PCIe-attached FPGA devices to bypass conventional OS-level protections, emphasizing the importance of robust IOMMU enforcement and hardware-level defenses. Moving forward, research should focus on developing secure hardware designs and firmware protections against unauthorized DMA devices. The findings of this report establish the critical balance between security research and defense implementation.

References

- Markettos, A. T., & Moore, S. W. (2019). Thunderclap: Exploring vulnerabilities in operating system IOMMU protection via DMA from untrusted peripherals.

- Frisk, Ulf. PCILeech Documentation and GitHub Repository.

- Bosman, Erik, et al. “Dedup Est Machina: Memory Deduplication as an Advanced Exploitation Vector.” IEEE S&P, 2016.

- Rutkowska, J. “Subverting the Xen hypervisor.” Black Hat USA, 2008.

- Wojtczuk, R., & Rutkowska, J. (2011). Attacking Intel TXT via SMM memory corruption.

- Van Bulck, J., et al. “Foreshadow: Extracting the keys to the Intel SGX kingdom with transient out-of-order execution.” USENIX Security, 2018.

- Embleton, S., Sparks, S., & Zou, C. C. (2008). SMM rootkits: A new breed of OS independent malware.

- Stewin, P., & Bystrov, I. (2012). Understanding DMA malware.

- Inception Project, GitHub Repository.

- Intel, PCI Express Architecture Specifications.

- Xilinx FPGA PCIe IP Core Documentation.

- Intel FPGA Development Kit PCIe Design Guide.

- Peleg, A., & Wool, A. (2019). The Thunderclap attack on USB-C and PCIe.

- Wu, K., et al. (2018). Leveraging DMA for practical attacks on hypervisors.

- Huang, L., et al. (2021). DMA-based memory acquisition for forensic analysis.

You can download the Project files here: Download files now. (You must be logged in).

Responses